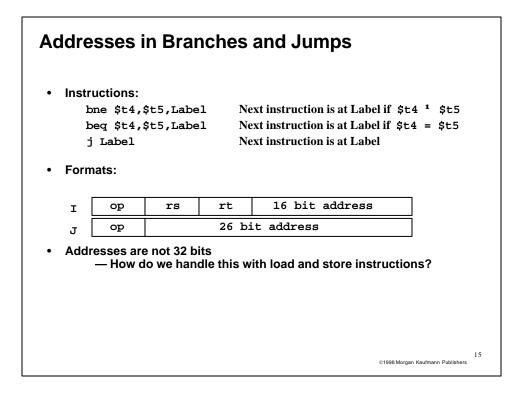

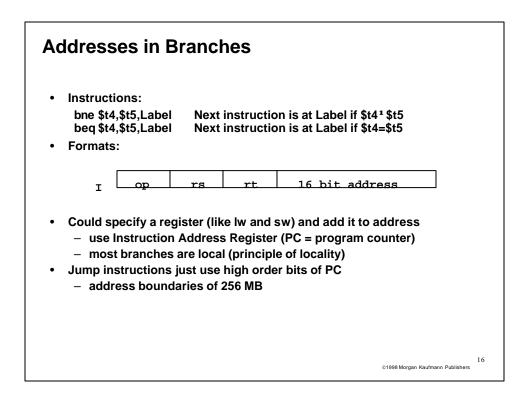

## **MIPS Instructions** Instruction Meaning add \$s1,\$s2,\$s3 \$s1 = \$s2 + \$s3sub \$s1,\$s2,\$s3 \$s1 = \$s2 - \$s3addi \$s1,\$s2,4 \$s1 = \$s2 + 4ori \$s1,\$s2,4 \$s2 = \$s2 | 4 lw \$s1,100(\$s2) s1 = Memory[s2+100]sw \$s1,100(\$s2) Memory[\$s2+100] = \$s1 bne \$\$4,\$\$5,Label Next instr. is at Label if \$\$4 1 \$\$5 beq \$\$4,\$\$5,Label Next instr. is at Label if \$\$4 = \$\$5 slt \$t1,\$s2,\$s3 if \$s2 < \$s3, \$t1 = 1 else \$t1 = 0 j Label Next instr. is at Label Next instr is in register \$s1 jr \$s1 jal Label Jump and link procedure at Label 2 ©1998 Morgan Kaufmann Publishers

| Mach     | ine La                                           | ngua              | ige: R   | Form   | nat   |        |                                  |   |

|----------|--------------------------------------------------|-------------------|----------|--------|-------|--------|----------------------------------|---|

| -  <br>- | ructions,<br>Example:<br>registers<br>ruction Fo | add \$<br>have nu | t0, \$s1 | , \$s2 |       |        | 32 bits long                     |   |

|          | 000000                                           | 10001             | 10010    | 01000  | 00000 | 100000 |                                  |   |

|          | ор                                               | rs                | rt       | rd     | shamt | funct  |                                  |   |

| • RF     | ormat                                            |                   |          |        |       |        |                                  |   |

|          |                                                  |                   |          |        |       |        | ©1998 Morgan Kaufmann Publishers | 7 |

| Machine Language: J Format                                                                                                                                                                                                                                |                                       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|

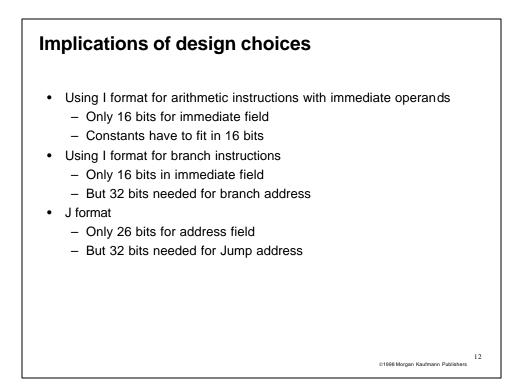

| <ul> <li>Jump (j), Jump and link (jal) instructions have two fi <ul> <li>Opcode</li> <li>Address</li> </ul> </li> <li>Instruction should be 32 bits (Regularity principle) <ul> <li>6 bits for opcode</li> <li>26 bits for address</li> </ul> </li> </ul> | ields                                 |

| J op 26 bit address                                                                                                                                                                                                                                       |                                       |

|                                                                                                                                                                                                                                                           | 9<br>©1998 Morgan Kaufmann Publishers |

|                                 | arize:                                         |            |                                                                                                                                                                                                                                                     |                                                                 |                                   |  |  |

|---------------------------------|------------------------------------------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|-----------------------------------|--|--|

|                                 |                                                |            | MIRS on                                                                                                                                                                                                                                             | orando                                                          |                                   |  |  |

| Name                            | Example                                        |            | MIPS operands<br>Comments                                                                                                                                                                                                                           |                                                                 |                                   |  |  |

| 32 registers                    | \$s0-\$s7, \$t0-\$t9, \$zero,                  |            | Fast locations for data. In MIPS, data must be in registers to perform<br>arithmetic. MIPS register \$zero always equals 0. Register \$at is<br>reserved for the assembler to handle large constants.                                               |                                                                 |                                   |  |  |

| 2 <sup>30</sup> memorv<br>words | Memory[0],<br>Memory[4],,<br>Memory[4294967292 | 2]         | Accessed only by data transfer instructions. MIPS uses byte addresses, so<br>seouential words differ bv 4. Memory holds data structures, such as arravs.<br>and snilled registers, such as those saved on procedure calls<br>MIPS assembly language |                                                                 |                                   |  |  |

| Category                        | Instruction                                    | Ex         | ample                                                                                                                                                                                                                                               | Meaning                                                         | Comments                          |  |  |

|                                 | add                                            | add \$s1,  |                                                                                                                                                                                                                                                     | \$s1 = \$s2 + \$s3                                              | Three operands; data in registers |  |  |

| Arithmetic                      | subtract                                       | sub \$s1,  | \$s2, \$s3                                                                                                                                                                                                                                          | \$s1 = \$s2 - \$s3                                              | Three operands; data in registers |  |  |

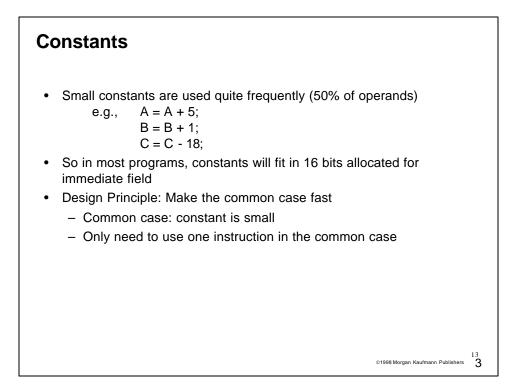

|                                 | add immediate                                  | addi \$s1, | \$s2, 100                                                                                                                                                                                                                                           | \$s1 = \$s2 + 100                                               | Used to add constants             |  |  |

|                                 | load word                                      | lw \$s1,   | 100(\$s2)                                                                                                                                                                                                                                           | \$s1 = Memory[\$s2 + 100                                        | Word from memory to register      |  |  |

|                                 | store word                                     | sw \$s1,   | 100(\$s2)                                                                                                                                                                                                                                           | Memory[\$s2+100] = \$s1                                         | Word from register to memory      |  |  |

| Data transfer                   | load byte                                      | lb \$s1,   | 100(\$s2)                                                                                                                                                                                                                                           | \$s1 = Memory[\$s2 + 100                                        | Byte from memory to register      |  |  |

|                                 | store byte                                     | sb \$s1,   | 100(\$s2)                                                                                                                                                                                                                                           | Memory[\$s2+100] = \$s1                                         | Byte from register to memory      |  |  |

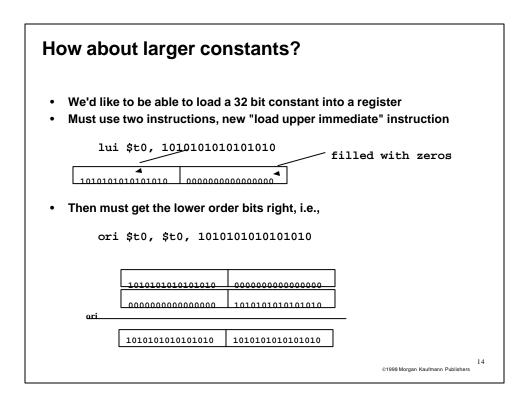

|                                 | load upper immediate                           | lui \$sl,  | 100                                                                                                                                                                                                                                                 | \$s1 = 100 * 2 <sup>16</sup>                                    | Loads constant in upper 16 bits   |  |  |

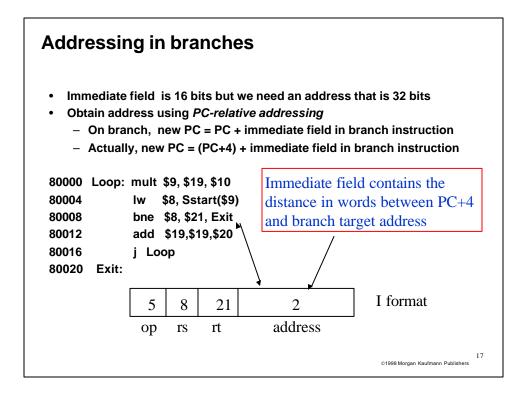

|                                 | branch on equal                                | beq \$s1,  | \$s2, 25                                                                                                                                                                                                                                            | if (\$s1 == \$s2) go to<br>PC + 4 + 100                         | Equal test; PC-relative branch    |  |  |

| Conditional                     | branch on not equal                            | bne \$sl,  | \$s2, 25                                                                                                                                                                                                                                            | if ( <sup>\$s1</sup> != <sup>\$s2</sup> ) go to<br>PC + 4 + 100 | Not equal test; PC-relative       |  |  |

| branch                          | set on less than                               | slt \$sl,  | \$s2, \$s3                                                                                                                                                                                                                                          | if(\$s2 < \$s3) \$s1 = 1;<br>else \$s1 = 0                      | Compare less than; for beq, bne   |  |  |

|                                 | set less than<br>immediate                     | slti \$s:  | L, \$s2, 100                                                                                                                                                                                                                                        | if(\$s2 < 100) \$s1 = 1;<br>else \$s1 = 0                       | Compare less than constant        |  |  |

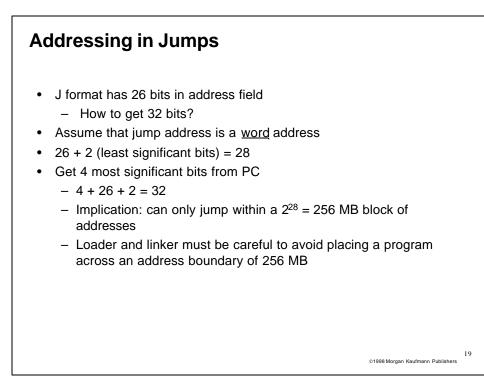

|                                 | jump                                           | j 2500     | )                                                                                                                                                                                                                                                   | go to 10000                                                     | Jump to target address            |  |  |

| Uncondi-                        | jump register                                  | jr \$ra    |                                                                                                                                                                                                                                                     | go to \$ra                                                      | For switch, procedure return      |  |  |

| tional jump                     | iump and link                                  | ial 2500   |                                                                                                                                                                                                                                                     | \$ra = PC + 4; go to 10000                                      | For procedure call                |  |  |

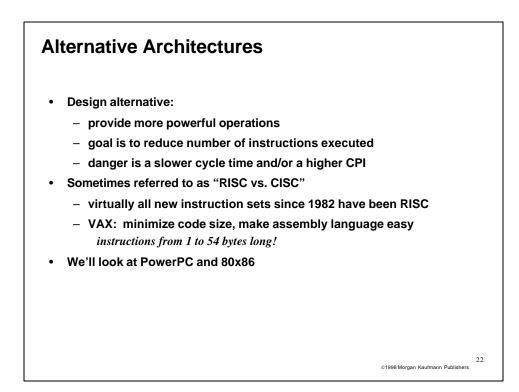

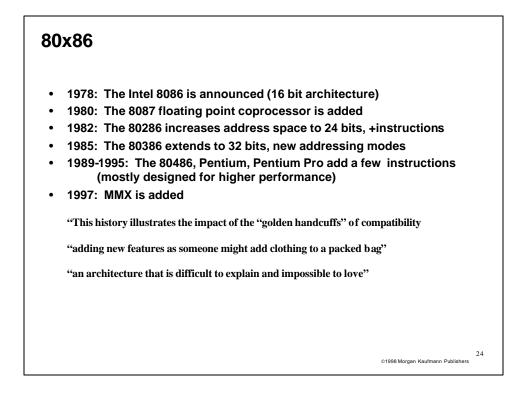

## A dominant architecture: 80x86

- See your textbook for a more detailed description

- Complexity:

- Instructions from 1 to 17 bytes long

- one operand must act as both a source and destination

- one operand can come from memory

- complex addressing modes

- e.g., "base or scaled index with 8 or 32 bit displacement"

- Saving grace:

- the most frequently used instructions are not too difficult to build

- compilers avoid the portions of the architecture that are slow

"what the 80x86 lacks in style is made up in quantity, making it beautiful from the right perspective"

## 25 ©1998 Morgan Kaufmann Publishers

## Summary

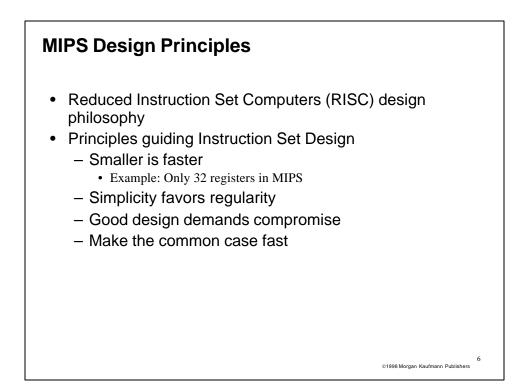

- Design Principles:

- simplicity favors regularity

- smaller is faster

- good design demands compromise

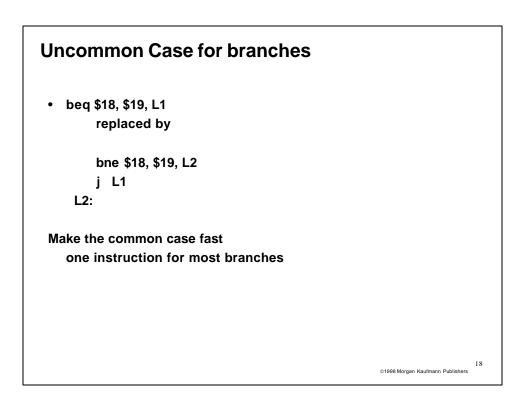

- make the common case fast

26 ©1998 Morgan Kaufmann Publishers