| — ра             |                 |         | ?)                 |

|------------------|-----------------|---------|--------------------|

| Device           | Behavior        | Partner | Data rate (KB/sec) |

| Keyboard         | input           | human   | 0.01               |

| Mouse            | input           | human   | 0.02               |

| Voice input      | input           | human   | 0.02               |

| Scanner          | input           | human   | 400.00             |

| Voice output     | output          | human   | 0.60               |

| Line printer     | output          | human   | 1.00               |

| Laser printer    | output          | human   | 200.00             |

| Graphics display | output          | human   | 60,000.00          |

| Modem            | input or output | machine | 2.00-8.00          |

| Network/LAN      | input or output | machine | 500.00-6000.00     |

| Floppy disk      | storage         | machine | 100.00             |

| Optical disk     | storage         | machine | 1000.00            |

| Magnetic tape    | storage         | machine | 2000.00            |

| Magnetic disk    | storage         | machine | 2000.00-10,000.00  |

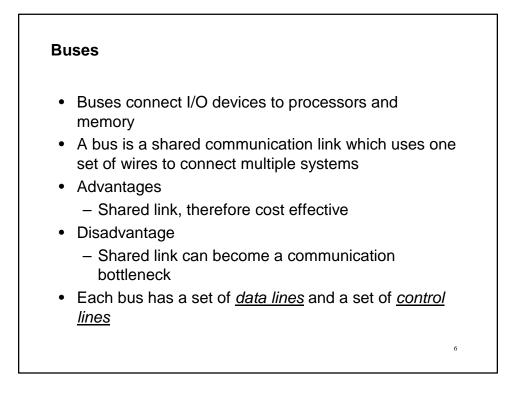

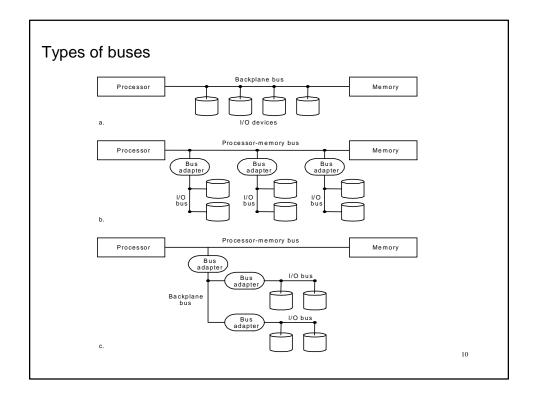

## Types of buses

- Processor-Memory bus

- Short

- High-speed

- Matched to the memory system

- I/O buses

- Lengthy

- Can have many different devices attached to them

- Wide range of data transfer speeds

- Backplane buses

- Can have processor, memory, I/O devices coexisting on a single bus

- Balance demands of processor-memory communication with demands of device memory communication

Synchronous and Asynchronous Buses

- Synchronous

- Driven by a clock

- Clock input to control lines

- Protocol for communication is relative to this clock

- Example: processor-memory communication

- Processor sends address and read command in first clock cycle

- Memory sends data on fifth clock cycle

- Protocol is predetermined and driven by the clock

- Disadvantage

- Every device on bus must be able to run at same clock rate

- · Synchronous buses have to be short to avoid clock skew

12

11